### Design and behavioral simulation of comparator based switched-capacitor circuits

Carsten Wulff, Trond Ytterdal

Department of Electronics and Telecommunication Norwegian University of Science and Technology

# Outline

- Motivation

- Comparator based switched capacitor circuits

- Design equations

- Example of a comparator-based switched-capacitor circuit

- Future work

## **Motivation: Why CBSC**

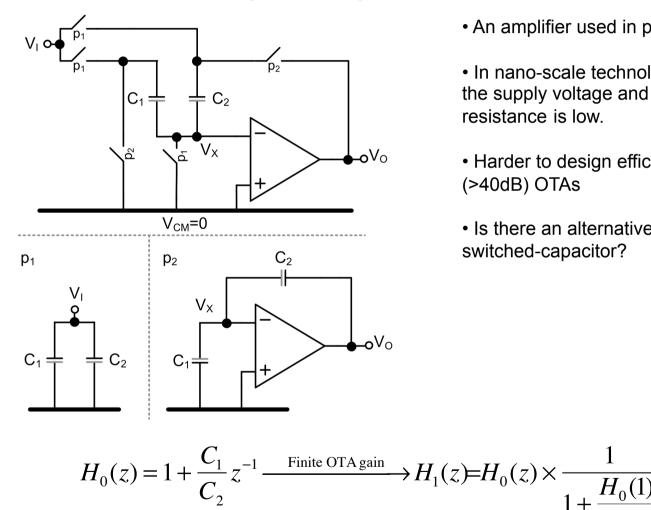

#### **Conventional switched-capacitor amplifier**

An amplifier used in pipelined ADCs

In nano-scale technologies (< 100nm)</li> the supply voltage and transistor output resistance is low.

- Harder to design efficient high-gain (>40dB) OTAs

- Is there an alternative to OTA based switched-capacitor?

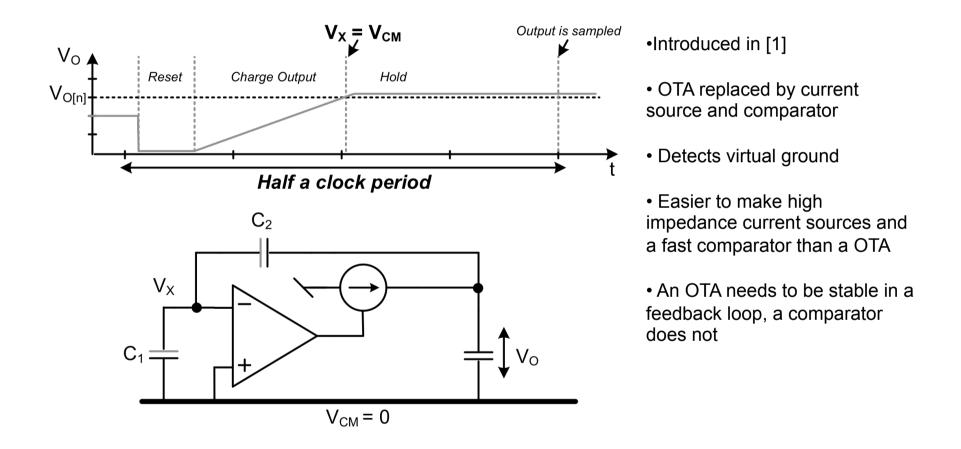

#### **Comparator-based switched capacitor circuits**

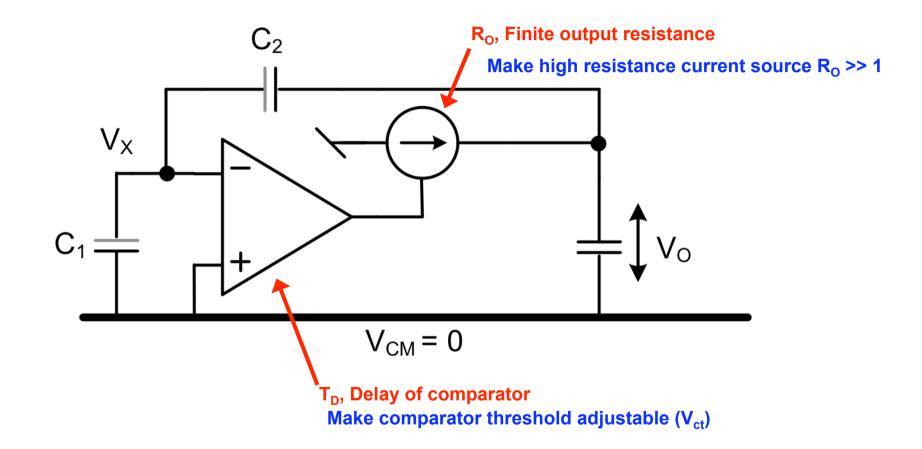

### **Non-ideal effects**

### The design equations

With these two effects the output voltage of the CBSC • amplifier is

$$V_{O} = 2e^{\frac{-T_{d}}{R_{O}C_{O}}} + I_{O}R_{O}\left[1 - e^{\frac{-T_{d}}{R_{O}C_{O}}}\left(1 + 2\frac{V_{ct}}{I_{O}R_{O}}\right)\right]$$

Gain of amplifier

Overshoot caused by comparator delay

$$C_{I} = C_{O}$$

1. Required sampling capacitor (from [2]) 3. Required output resistance

$$C = a_1 \frac{48kT2^{2B}}{V_{pp}^{2}}$$

- $R_{O} = \frac{-T_{d}}{\ln(1 \varepsilon_{a})C_{O}}$

- T = Temperature a₁ = constant T<sub>r</sub> = reset time

2. Necessary current

$$I_{o} = C_{o} \frac{(V_{pp}/4 + V_{cm})}{1/2f_{s} - T_{r}}$$

$$V_{ct} = -\frac{1}{2} I_O R_O \left( 1 - e^{\frac{T_d}{R_O C_O}} \right)$$

$\varepsilon_{a}$  = Gain error  $V_{PP}^{\flat}$  = Peak to peak output voltage **B** = Number of bits k = Boltzmann's constant V<sub>cm</sub> = Common mode voltage f<sub>s</sub> = sampling frequency

Calculate:

- I<sub>o</sub> = Current in current source

- **R**<sub>o</sub> = Output resistance

- **C** = Sampling capacitor

- V<sub>ct</sub> = Comparator threshold

### The example system

#### Given

| Parameter       | Value    |

|-----------------|----------|

| В               | 9        |

| Т               | 300K     |

| k               | 1.38e-23 |

| a <sub>1</sub>  | 3        |

| V <sub>PP</sub> | 1V       |

| V <sub>CM</sub> | 0.6V     |

| ε <sub>g</sub>  | 1/(2^B)  |

| T <sub>d</sub>  | 0.5ns    |

| T <sub>r</sub>  | 1ns      |

| fs              | 50MHz    |

#### Calculated

| Parameter       | Value |

|-----------------|-------|

| С               | 160fF |

| I <sub>o</sub>  | 30µA  |

| R <sub>o</sub>  | 1.1MΩ |

| V <sub>ct</sub> | 32mV  |

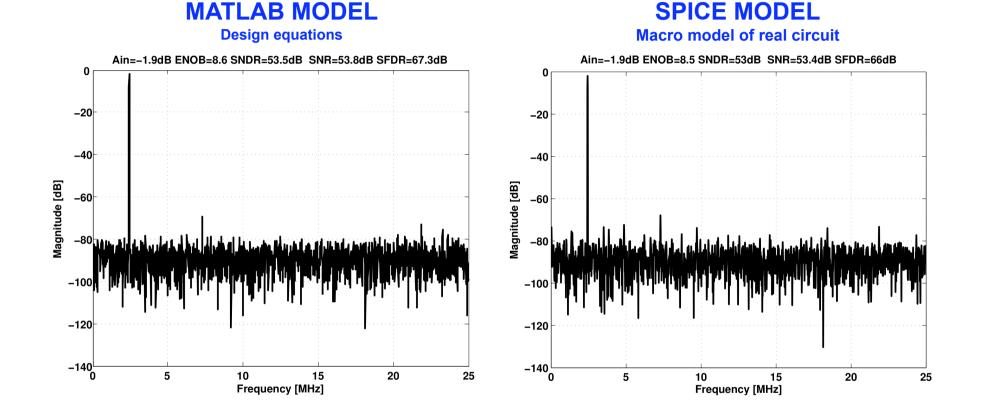

### **Simulation results**

#### < 7 % Difference for SNDR and SNR

Both models can be downloaded from <u>http://www.wulff.no/carsten</u>. Tools & Scripts, Behavioral model of comparator-based switched-capacitor circuits

# Conclusion

- Design equations give can quickly produce values for macro model simulation

- Design equations predicts the required parameters with high accuracy (less than 7% error for SNDR and SNR)

### References

- T. Sepke, J. K. Fiorenza, C. G. Sodini, P. Holloway, and H.-S. Lee, "Comparator-based switched-capacitor circuits for scaled CMOS technologies," in ISSCC Digest of Technical Papers, 2006, pp. 220–221.

- C. Wulff and T. Ytterdal, "Design Of A 7-bit, 200MS/s, 2mW Pipelined ADC With Switched Open-Loop Amplifiers In A 65nm CMOS Technology," in Proc. NORCHIP 2007